プロセッサ―コンピュータの制御・演算装置の知識

プロセッサはコンピュータの制御・演算装置です。プロセッサ関連の知識をまとめています。

目次

このページの目次です。

1. プロセッサとは

2. コンピュータの種類

3. コンピュータの構成

4. プロセッサの種類

5. プロセッサの基本的な仕組み

6. プロセッサのアーキテクチャ

7. プロセッサの構造と方式

8. プロセッサの動作原理

9. マイクロプログラム制御

10. プロセッサの性能

11. プロセッサの高速化技術

12. 並列処理

13. マルチプロセッサシステム

1. プロセッサとは

コンピューターの制御・演算を行う処理装置のことをプロセッサといいます。CPUやMPUなどはプロセッサーの一つです。

2. コンピュータの種類

代表的なコンピュータの種類と特徴についてまとめました。

3. コンピュータの構成

コンピュータを構成する基本的な構成要素と、その中心であるプロセッサの基本的な仕組み、機能および性能の考え方を理解するためまずはコンピュータの構成についてまとめています。

コンピューターの五大機能・装置

コンピュータは、入力、記憶、演算、制御、出力の五つの機能・装置に分類されます。これら、コンピューターの五大機能(五大装置)について説明していきます。

4. プロセッサの種類

プロセッサの種類、それぞれの基本的な特徴、用途についてまとめています。

5. プロセッサの基本的な仕組み

プロセッサの基本的な仕組み、機能及び性能の考え方についてまとめています。

6. プロセッサのアーキテクチャ

プロセッサのアーキテクチャについてまとめています。

7. プロセッサの構造と方式

プロセッサの構造と方式についてです。

アキュムレータ

アキュムレータとは、論理演算や四則演算などを行う際に使われる演算専用のレジスタです。 英語はaccumulatorです。

補数器

補数の演算を行う回路を補数器といいます。

乗算器

乗算器は、二つの数についての乗算を行うための電子回路です。

積和演算器

積和演算器は、積和演算を行うための電子回路です。

命令アドレスレジスタ(命令カウンタ、プログラムカウンタ、逐次制御カウンタ)

命令アドレスレジスタは、次に実行すべき命令が格納されているメモリ上の番地(アドレス)を保存しているレジスタです。 命令カウンタ、プログラムカウンタ、逐次制御カウンタなどともいいます。

IR ( Instruction Register:命令レジスタ)

命令レジスタは、実行する命令の内容を格納するレジスタです。

GR(General Register:汎用レジスタ)

汎用レジスタは、状況に応じて様々な用途に用いることができるレジスタです。

インデックスレジスタ(指標レジスタ)

インデックスレジスタは、アクセスしたいメモリ上の番地(アドレス)の、基準値からの相対的な値を格納するためのレジスタです。 指標レジスタともいいます。

ベースレジスタ

ベースレジスタは、アクセスしたいメインメモリ上の番地(アドレス)の基準値や先頭位置を記憶しておくためのレジスタです。

MAR(Memory Address Register:メモリアドレスレジスタ)

メモリアドレスレジスタは、メインメモリ上の番地(メモリアドレス)を指定するために用意されたレジスタです。

DR(Data Register:データレジスタ)

データレジスタは、数値データを格納することができるレジスタです。

MR(Memory Register:メモリレジスタ)

メモリレジスタは、メインメモリから読み出されたデータを格納したり、書き込むデータを格納するレジスタです。

スタックポインタ

スタックポインタは、スタックと呼ばれるメモリ領域の現在の操作位置を保持するためのレジスタです。

8. プロセッサの動作原理

演算の仕組みや命令とアドレッシング、割込みなど、プロセッサの動作原理についてです。

演算の仕組み

AND回路、OR回路、NOT回路などの基本となる論理回路の組合せによって半加算器、全加算器が実現され、演算が行われています。

順序回路

順序回路は、過去に入った情報と現時点に入った情報との組合せで決まる論理回路です。

組合せ回路

組合せ回路は、出力がそのときの入力の状態のみで決まる論理回路です。

NAND回路

NAND回路は、否定論理積の演算を行う論理回路で、全ての入力の論理積(AND)をとったものの反転(NOT)する論理回路です。

命令とアドレッシング

代表的な機械語命令の種類について見ていきます。

算術演算命令

算術演算命令は、加算、減算、乗算、除算の四則演算など数値的な演算を行うための命令です。

論理演算命令

論理演算命令とは、論理演算における論理積(AND)、論理和(OR)、排他的論理和(XOR)、否定(NOT)の各命令のことをいいます。

転送命令

転送命令は、メインメモリーからレジスタ、レジスタからメモリーなどにデータを転送する命令です。

比較命令

比較命令は、レジスタやメモリの値の比較を行うための命令です。

分岐命令

分岐命令は、条件分岐を行う命令です。ジャンプ命令ともいいます。

シフト命令

シフト命令は、シフトを行う命令です。

入出力命令

入出力命令は、外から入力を受け付けたり、出力したりするときに使用される命令です。

アドレス部(オペランド)

アドレス部は、機械語で記述された命令のうち、アドレスが記されている部分のことをいいます。

オペランド

オペランドは、コンピュータの演算における値や変数のことをいいます。

フェッチ

フェッチは、機器やプログラムなどが特定の場所からデータなどを読み出す動作のことをいいます。

アドレス計算

アドレス計算は、オペランドの保存場所を導き出すことをいいます。

アドレス方式

アドレス方式は、アドレス計算を行う方式です。

アドレス修飾

アドレス修飾は、機械語命令のオペランドにあるアドレス情報を利用して、実行するべき命令の対象となるデータアドレスを決定することをいいます。

直接アドレス指定

直接アドレス指定は、データを取得する実際のメモリアドレス(有効アドレス)として、命令文の一部として記述された数値をそのままメモリ上の番地と解釈して用いる方式です。

間接アドレス指定

間接アドレス指定方式は、オペランド部に対象データの場所を示すメモリのアドレスが格納されている方式です。

インデックスアドレス指定(インデックス修飾)

インデックスアドレス指定は、データを取得する実際のメモリアドレス(有効アドレス)として、CPU内部の記憶装置の一種であるインデックスレジスタに保存された値と命令のアドレス部の値を足し合わせたものを用いる方式です。

インデックス修飾

インデックス修飾は、命令のアドレス部で指定されたメモリアドレスにインデックスレジスタの値を加算したものを実効アドレスとする方式です。

ベースアドレス指定

ベースアドレス指定は、アドレス部分を2つに分割し、ベースレジスタと呼ばれるレジスタとアドレスを示す部分に分け、実行アドレスがベースレジスタの内容とアドレスとの和となる方式です。

相対アドレス指定

相対アドレス指定は、アドレス部の値と、プログラムカウンターの値との和が有効アドレスである方式です。

絶対アドレス指定

絶対アドレス指定は、データを取得する実際のメモリアドレス(有効アドレス)として、命令文の一部として記述された数値をそのままメモリ上の番地と解釈して用いる方式です。

即値アドレス指定

即値アドレス指定は、オペランド部に対象となるデータそのものが入っている方式です。

有効アドレス(実効アドレス)

有効アドレスは、実効アドレスとも言い、制御装置が命令を実行する際に、実際に使用するアドレスのことをいいます。

割込み

割込みについてです。

SVC(SuperVisor Call)割込み

SVC割り込みとは、内部割込みの一種でプログラム自身があえて発生させる割込みです。

入出力割込み

入出力割込みとは、外部割り込みの一種で入出力が完了したときなどに発生する割込みです。

割込み制御

割込み制御は、割込み処理をコントロールする機構です。

マシンチェック割込み

マシンチェック割込みは、機械チェック割込みとも言い、外部割り込み機能のひとつで、ハードウェアに異常が検出された際に発生する割込みです。

プログラム割込み

プログラム割込みは、桁あふれ(オーバフロー、アンダフロー)や0による除算、記録保護違反など、プログラム上のエラーによって発生する内部割込みです。

9. マイクロプログラム制御

プロセッサの動作を制御する仕組みとして、1機械語命令を実行するためのプログラム(マイクロプログラム)をファームウェア化して内蔵する方式があります。

マイクロプログラムメモリ

マイクロプログラム制御ユニットは、制御信号を生成するためにソフトウェアアプローチを使用します。 制御信号の生成はプログラムの助けを借りて決定されます。 このプログラムは、より小さく高速なプロセッサの特別なメモリに格納されます。 このメモリをマイクロプログラムメモリまたはコントロールストアといい、プログラムをマイクロプログラムといいます。

マイクロプログラムメモリは英語で「microprogram memory」です。

マイクロプログラムカウンター

マイクロプログラムカウンタは、制御シーケンスを循環させるために使用されます。 条件は、マイクロプログラムのフローを決定するために使用されるビットです。 次のアドレスによって、次に実行されるマイクロワードが決まります。

エミュレーション

エミュレーションは、マイクロプログラム方式のコンピュータで、他のコンピュータの命令をマイクロプログラムで実現し、 他のコンピュータ用に作られたプログラムをすべてそのままそのコンピュータのうえで実行させることをいいいます。

水平型マイクロコード

水平型マイクロコード(マイクロプログラム)は、マイクロ命令が直接CPU各部の制御を行う方式のマイクロコードです。

垂直型マイクロコード

垂直型マイクロコード(マイクロプログラム)は、マイクロ命令を論理回路で解釈(デコード)して実行する方式のマイクロコードです。

10. プロセッサの性能

プロセッサの性能は、内部時計の速さや、単位時間に実行できる命令数などで表されます。 プロセッサの性能に関連するクロック周波数、MIPS(Million Instruction Per Second)、CPI(Cycles Per Instruction)の意味、関係式などプロセッサの性能指標についてをまとめています。

11. プロセッサの高速化技術

プロセッサの代表的な高速化技術について見ていきます。

パイプライン(命令パイプライン)

パイプライン処理方式とは、命令の実行を「取出し」と「実行」など、命令の処理工程(ステージ)に分け、ある命令のステージと次の命令のステージを並列に行う処理方式です。 パイプライン処理方式は、複数の命令をオーバーラップさせて同時実行可能とすることから、命令パイプラインとも呼ばれます。

パイプライン処理方式の制御イメージ

例えば、RISCマシンは、ステージ1(IF:命令フェッチ)、ステージ2(ID:命令デコード)、ステージ3(EX:実行)、ステージ4(MEM:メモリアクセス)、ステージ5(WB:レジスタ・ライトバック)の5段階にステージに分割されていて、 これをパイプライン処理にすると表のようなイメージで実行されます。

| サイクル1 | サイクル2 | サイクル3 | サイクル4 | サイクル5 | サイクル6 | ||

|---|---|---|---|---|---|---|---|

| 命令1 | IF | ID | EX | MEM | WB | ||

| 命令2 | IF | ID | EX | MEM | WB | ||

| 命令3 | IF | ID | EX | MEM |

スーパパイプライン

パイプラインを更に細分化することによって、高速化を図る方式です。

スーパスカラ

スーパースカラは、複数のパイプラインを用い、同時に複数の命令を実行可能にすることによってCPUやMPUなどプロセッサーを高速化する方式です。

VLIW

VLIWとは、Very Long Instruction Wordの略で、 同時に実行可能な複数の命令をまとめて一つの命令として、同時に実行し、プロセッサの実行効率を上げる方式です。

VLIWは、プロセッサの高速化技法の一つとして、同時に実行可能な複数の動作を、 コンパイルの段階でまとめて一つの複合命令とし、高速化を図ります。

CPUの命令セットの中で、 同時に実行しても互いに影響しない複数の命令を組み合わせ、 一つの長い命令語とすることで、 並列実行におけるパイプラインの効率化を図る手法で 命令語を長く取り、一つの命令で複数の機能ユニットを同時に制御することによって高速化を図ります。

ベクトル処理方式

ベクトル処理方式は、一つの命令を同時に複数のデータに適用する方式です。

ハイパースカラ方式

ハイパースカラ方式は、命令パイプライン処理方式、スーパースカラ方式、VLIW方式および、ベクトル処理方式の短所を無くして長所を包括的にまとめた命令レベル処理方式です。

超並列プロセッサ

超並列プロセッサ (MPP) は、ネットワークを介して大規模なタスクを迅速に達成するために、コンピュータのコレクションを相互にリンクする技術です。

パイプラインハザード

パイプラインハザードは、マイクロプロセッサのパイプライン処理で発生する問題の一つで、命令間の依存関係などによりパイプライン処理を止めたりやり直さなければならなくなることをいいます。

データハザード

データハザードは、プログラムの実行速度を遅くする要因となるもので、CPUがプログラムを実行する際に現れる問題の1つです。

構造ハザード

構造ハザードは、複数の命令をパイプラインで並行に処理する過程で、同じタイミングで同じハードウェア資源にアクセスしようとするなど競合が発生し、処理がつっかえることをいいます。

制御ハザード

制御ハザードは、複数の信号が同時に発生した場合、回路の出力が予期しない値を出力することをいいます。

シングルコアプロセッサ

シングルコアプロセッサは、1つのプロセッサコアを搭載したプロセッサです。

マルチコアプロセッサ

マルチコアプロセッサは、2つ以上のプロセッサコアを1個のパッケージに集積したプロセッサです。

マルチスレッディング

マルチスレッディングは、マルチコアプロセッサのシングルコアが、OSによってサポートされている、複数の実行スレッドを同時に提供する機能のことです。

12. 並列処理

代表的な並列処理方式について見ていきます。

SISD

SISDは、Single Instruction stream, Single Data streamの略で、シングルプロセッサのコンピュータアーキテクチャです。 単一の命令ストリームを実行し、一度に1つのデータだけを操作する方式で、ノイマン型アーキテクチャに対応しています。

SIMD

SIMDとは、読み方はシムド、1つの命令で複数のデータを処理する方式です。

MISD

MISDは、Multiple Instruction stream, Single Data streamの略で、並列コンピューティングアーキテクチャです。 多数の機能ユニットが同じデータに対して異なる操作を同時に行います。

MIMD

MIMDとは、Multiple Instruction stream/Multiple Data streamの略で、代表的な並列処理方式の1つです。

13. マルチプロセッサシステム

複数のプロセッサを搭載し,高速化及び高信頼化を実現したシステムについて見ていきます。

疎結合マルチプロセッサシステム

疎結合マルチプロセッサシステムは、マルチプロセッサシステムの構成法の一つで、複数のプロセッサがそれぞれメインメモリなどを持ち、別々のOSインスタンスによって動作します。

密結合マルチプロセッサシステム

密結合マルチプロセッサシステムは、複数のプロセッサーが主記憶やディスクなどの資源を共有し、互いに連絡をとりながら1つのOSによって制御されるマルチプロセッサーシステムです。

アムダールの法則

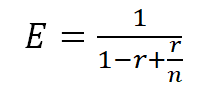

アムダールの法則は、システムの処理性能改善に関する法則です。 アムダールの法則は、以下のような数式で表されます。

並列化によってrは高速できる割合、nはCPUの数、EがCPUを増やすことによって得られる計算速度向上の程度を示しています。

同期

同期は、時系列的にタイミングを合わせる制御のことを意味する用語です。 マルチプロセッサシステムのキャッシュメモリは、MESIプロトコルなどのキャッシュコヒーレンシプロトコルを使用して内容を同期させて一貫性を保ちます。

クラスタ

クラスタは、一つのシステムとして処理を実行するひとまとまりの複数のコンピュータ群です。 この技術の発展形としてクラウドコンピューティングがあります。

更新履歴

- 2023/7/31 プロセッサの高速化技術について追記しました。

- 2023/3/19 マイクロプログラム制御について追記しました。

- 2022/9/10 割込みについて追記しました。

- 2022/8/23 命令とアドレッシングについて追記しました。

- 2022/8/16 プロセッサの構造と方式について追記しました。

- 2022/8/13 命令セットについて追記しました。

- 2022/7/27 命令形式について追記しました。

- 2022/7/19 データ処理の単位について追記しました。

- 2022/5/14 コンピュータの種類について追記しました。

- 2021/11/11 マルチプロセッサシステムについて追記しました。

- 2021/11/8 並列処理について追記しました。

- 2021/10/27 プロセッサの高速化技術について追記しました。

- 2021/9/21 プロセッサの動作原理について追記しました。

- 2021/9/13 プロセッサの構造と方式について追記しました。

- 2021/9/8 プロセッサのアーキテクチャについて追記しました。

- 2021/8/23 プロセッサの種類について追記しました。

- 2021/8/15 コンピュータの種類について追記しました。

- 2021/7/30 プロセッサの基本的な仕組みについて追記しました。